3D集成工艺简介

时间:2020-07-02 已阅读:10382次

引言:自摩尔定律首次预测硅片上晶体管的数量以18个月为周期翻一番以来,随着晶体管密度的增加,按比例缩小的发展已经接近极限。为了保证在芯片面积不变的前提下提升芯片性能,增加器件的数量,减小引线延迟对性能的影响,降低功耗,同时也为了满足新的应用需求(在系统中集成多种非电子功能,如射频、光/光电、MEMS等),3D集成已经成为关键的解决方案之一。

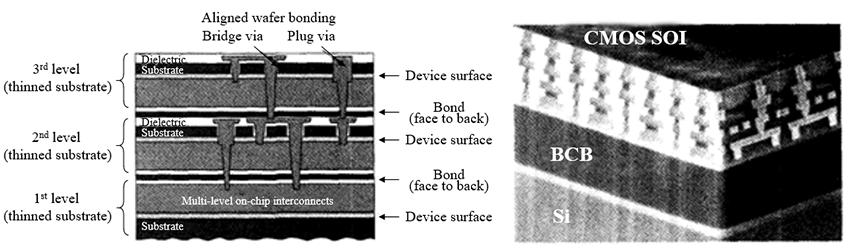

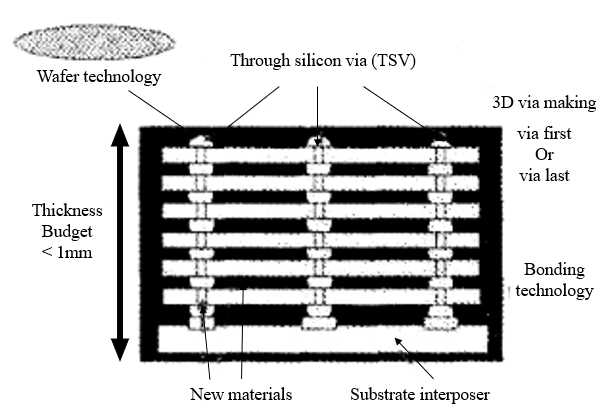

3D集成可以定义为堆叠和垂直互联的器件层的制造,是一种系统级架构,即将多层平面器件堆叠起来,器件层之间通过穿透硅的Z方向通孔(Through Silicon Via, TSV)来实现垂直互联,使其在Z轴方向上形成立体集成和信号连通,如图1所示。

图1 三维堆叠芯片结构示意图

系统从平面放置到垂直堆叠的转变很大程度缩短了互联长度,在互联方式上,先后经历了引线键合(Wire Bonding)、倒装芯片(Flip Chip)和硅通孔技术(Through Silicon Via, TSV),随着发展,互联长度不断降低,芯片利用率不断提高,TSV更是将3D集成的概念充分体现。

引线键合

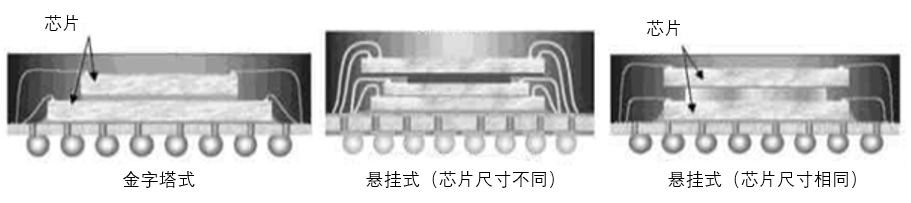

采用引线键合方法的3D集成是将不同的堆叠芯片利用一个共用的插入板或封装互联,每个芯片通过引线键合连接到插入板。引线键合的主要缺点是紧密放置的引线之间存在很大的电感耦合,性能受到互联长度的制约,不适合高频、高速电路。引线键合是3D 集成的初期型态,目前仍广泛应用于SiP (System-in-Package)领域。

图2 引线键合的不同方式

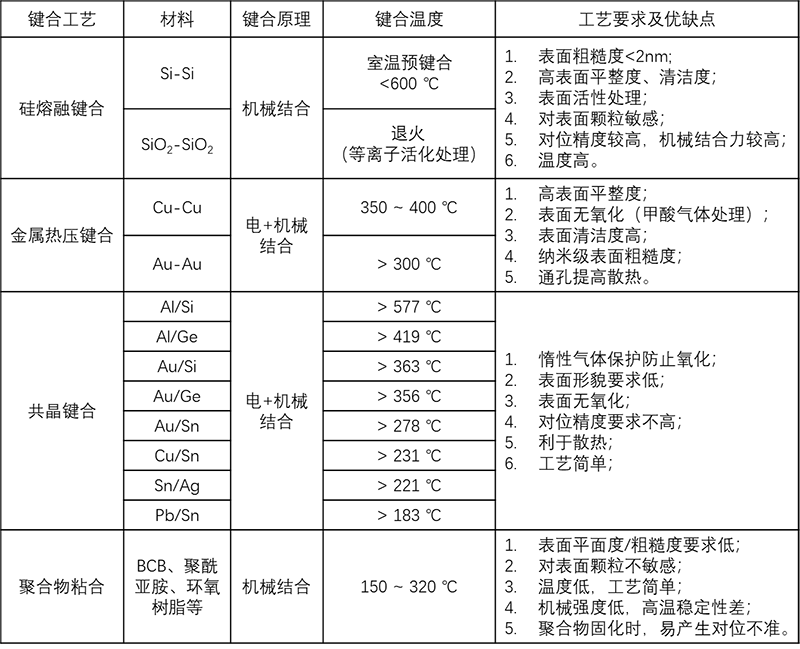

表 1键合技术及工艺特点

倒装芯片

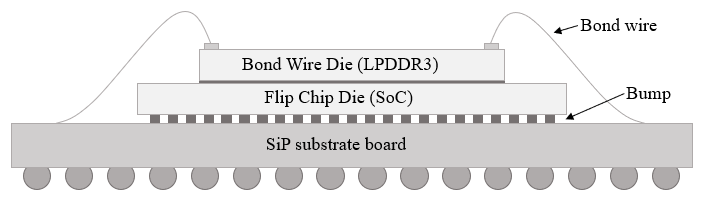

倒装芯片常采用混合芯片堆叠方式,即倒装芯片互联与引线键合组合,顶层芯片倒装可以消除到基板的长引线链接,常用于芯片间通信,具有高频运行、低寄生效应、高I/O密度、小型化等优点。底层芯片倒装有利于芯片高速运行,这种方法将基板互联分为两个区域,芯片下部用于倒装芯片,芯片之外用于引线键合,提高了基板的使用率,但顶部芯片的引线键合仍然有高寄生效应。倒装芯片这种3D(或称之为2.5D)解决方案在手机等移动设备中比较常用。

图3 倒装芯片示意图

TSV技术

TSV技术通过铜、钨、多晶硅等导电物质的填充,实现硅通孔的垂直电气互连。TSV可以通过垂直互连减小互联长度以及提高互联密度,从而获得更好的互联性能,减小信号延迟,降低电容/电感,实现芯片间的低功耗,高速通讯,增加宽带和实现器件集成的小型化。

图4采用硅通孔技术(TSV)的堆叠芯片

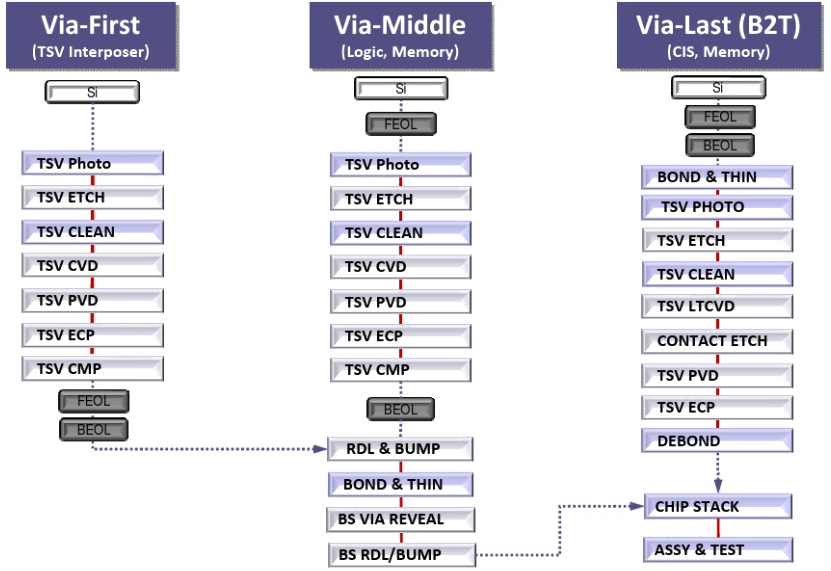

TSV的工艺主要包括通孔制作技术(激光钻孔(Laser Drill)、深反应离子刻蚀(DRIE)),通孔侧壁薄膜淀积技术(通孔侧壁绝缘层淀积技术、通孔侧壁粘附/扩散阻挡层及种子层金属淀积技术),通孔填充技术(电镀),化学机械研磨技术,晶圆减薄技术,去除和再分布引线(RDL)等工艺技术。TSV可以在IC制造的开始制作(Via-First),也可以在IC制造过程中制作(Vial-Middle),也可以在IC制造完成之后制作(Via-Last),如图5所示,展示了TSV的制作流程。TSV深孔填充技术是3D集成的关键技术,也是难度较大的一个环节,TSV填充效果直接关系到芯片的可靠性和良率等问题。另外,在基片减薄过程中保持良好的完整性,避免裂纹扩展是TSV工艺过程中的另一个难点。随着产业界的推动,3D集成工艺中的热管理、热机械应变和连接密度等难题都已有相应的解决办法。迄今为止,TSV大多应用于图像传感器、存储器、高端FPGA和少数MEMS设备等产品。

图5 TSV制造流程

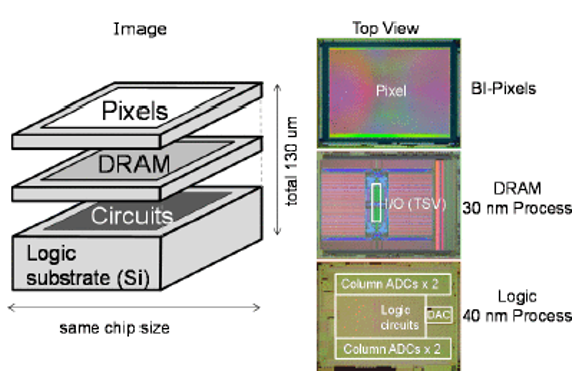

一种3层堆叠集成工艺CMOS图像传感器的原理图如图6所示,其截面图如图7所示,从图中可以看到顶层的像素层(Pixels 19.3M),中间的存储层(DRAM 1Gbit),下层的逻辑层(Logic),点划线标明了其分界面。通过两个TSV穿过了DRAM将Pixels和Logic相连接,如表2中所示,用到的TSV最小直径为2.5um,最小周期为6.3um,宽度为2um,整个传感器阵列使用到了约35000个TSV用以层间互联。

图6 三层堆叠背照式CMOS图像传感器原理图

图7 三层堆叠背照式CMOS图像传感器截面图

表2 三层堆叠背照式CMOS图像传感器TSV参数

3D集成工艺现已成为高性能的半导体集成的解决方案,可以替代因光刻技术投资庞大而在未来一段时间内难以维持经济效益的标准"摩尔定律"。3D集成被选择背后的动因是性能、带宽、复杂性、互连密度,以及系统微缩化、最终成本和价值链。