传输线网络和阻抗分析

时间:2023-05-17 已阅读:8024次

随着电子科学技术的飞速发展,信号的传播速度也从最初的几赫兹到现代通讯太赫兹技术,特别是射频微波信号传输过程中会出现各种损耗和衰减等问题。如何从信号源、传输介质、接收端等方面改善和提高信号传输的质量已是当下硬件工程师的一大难题。本篇将从信号的传输介质逐步深入浅出的探讨信号在传输线的传输,并结合部分案例讲解不同网络下的阻抗网络匹配。

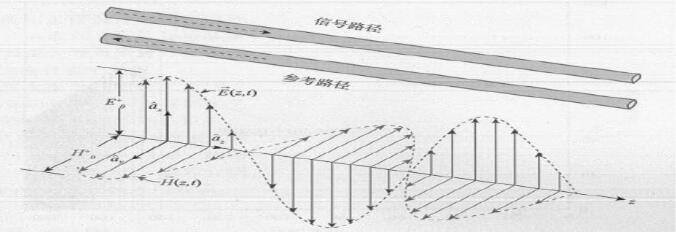

作为硬件工程师经常提起的传输线这一术语,简单的来讲传输线是由两条一定长度的导线组成的,传输线作为一种介质将信号从一端传导到另一端。将一条称为信号路径,另一条称为参考路径(有时也称为返回路径)。那如何才能更好更准确的理解传输线呢?一般有两种方法,一种是从电路的角度出发去讨论信号传输的阻抗,另一个从场的角度讨论传输的电磁场变化。

一、传输线阻抗理论:

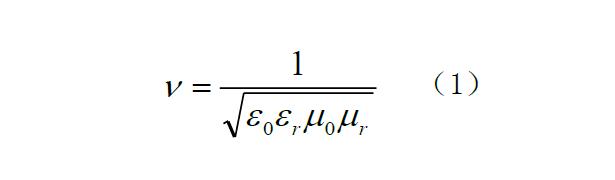

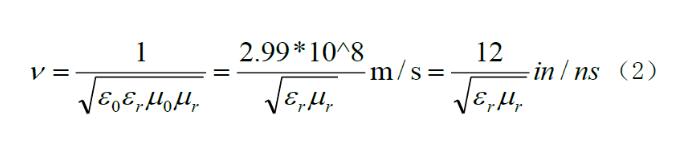

首先讨论一个简单的问题:传输线中信号的传输速度取决于导体中电子的速度吗?这个问题作为初学者常常会犯错。其实信号传输是传输介质中无数个自由电子的整体传递,并非某一个电子从传输线的一头移动到另一头。以常见的铜导线为例自由电子的速度约1cm/s,而常见的铜导线中信号的速度10^8m/s。那么对于一个信号在传输线中传播速度到底与哪些因素相关,从麦克斯韦方程组推导可得电磁场变化(或场链)的速度:

其中,Ɛ0为自由空间的介电常数(8.89*10^-12 F/m),表示材料的相对介电常数,µ0表示自由空间的磁导率(4π*10^-7 H/m),µr表示材料的相对磁导率(几乎所有的互连材料及不含铁磁体材料的聚合物,其磁导率都为1)。

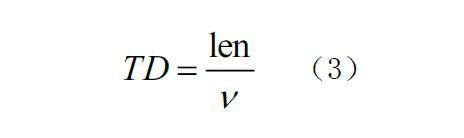

从物理学中,引入另外一个概念时延TD来表示信号的传播,它与互连线长度的关系为:

经验值:

当信号在FR4上长为6in的互连线中传输时,时延约为1ns;

时延迟速率约为1/6 in/ns=0.166ns/in(170ps/in);

对应0.5in长的BGA引线的连线时延为170ps/in * 0.5 in =85ps。

上述内容从电磁场的角度说明传输线的传输速度和时延,下面按照电学的角度即电阻(对于信号称作阻抗)来说明信号的传播。在信号完整信号中把信号每一步所感受到的阻抗称为瞬时阻抗,对于互联特征一致即均匀传输线又称为特征阻抗。

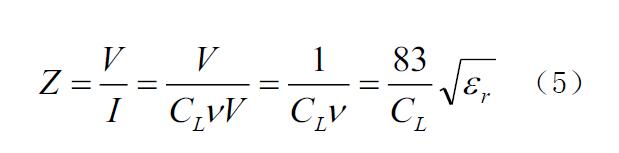

传输线的零阶模型把传输线的信号路径和返回路径等效一系列的电容器组成,对于均匀传输线,传输线的阻抗由横截面积和材质决定。

代入公式(2)可得,

其中,CL 表示单位长度电容量,v表示材料中的光速,Ɛ0为自由空间的介电常数(8.89*10^-12F/m)。

经验值:

对于介电常数为4,单位长度电容为3.3pF/in的传输线,特征阻抗为

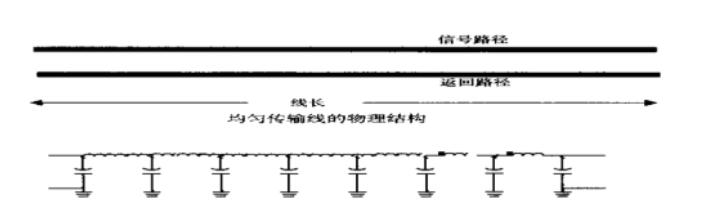

对于非理想即非恒定瞬时阻抗,引入传输线的一阶模型来计算传输线的阻抗。一阶模型把信号路径和返回路径导线的每一小节描述成小电容+小电感,每两个小电容被一个小回路电感隔开

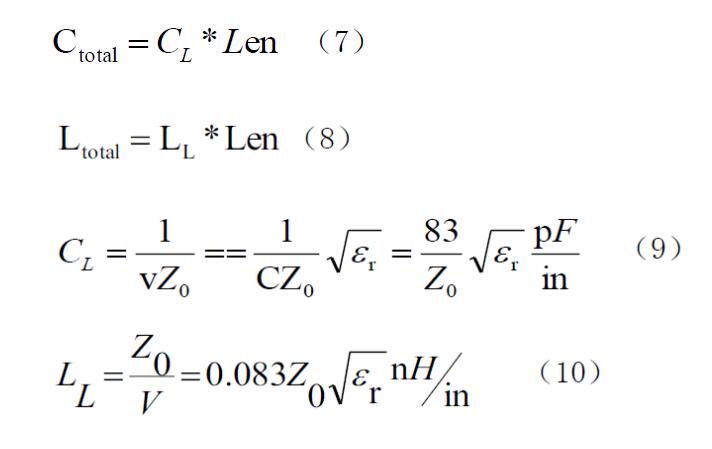

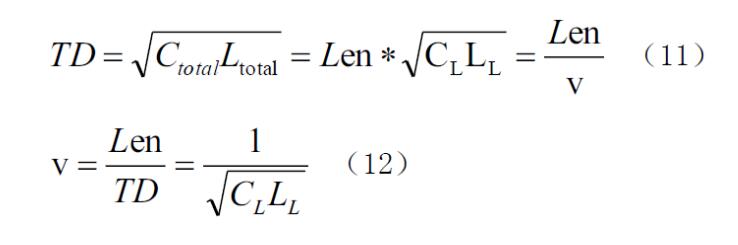

传输线的总长度Len,总电容和总电感为:

传输线的时延和传播速度:

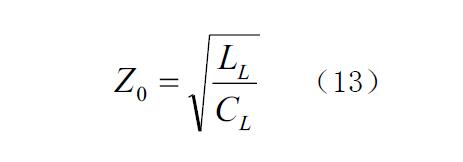

传输线的特征阻抗:

经验值:

传输线的特征阻抗为50Ω,介电常数为4,单位长度电容为:CL=83/50*2=3.3pF/in;

传输线的特征阻抗为50Ω,介电常数为4,单位长度电容为:LL=0.083* 50*2=8.3pF/in。

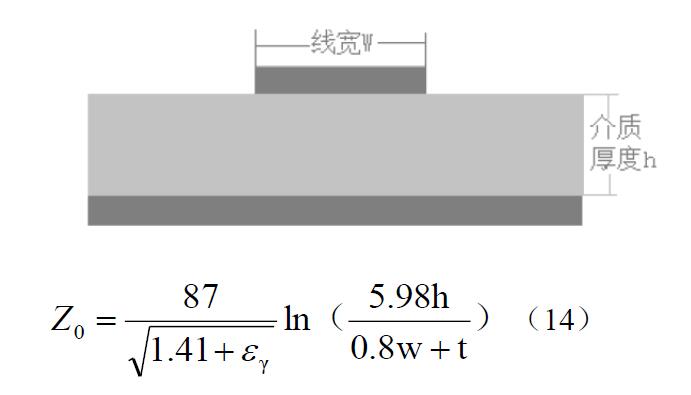

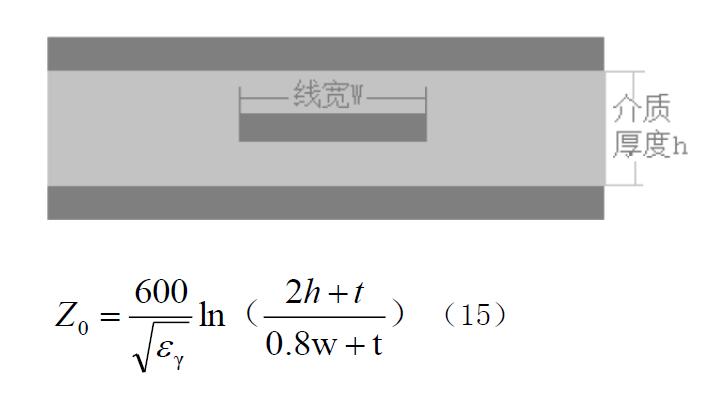

对于FR4板的微带线和带状线,IPC推荐的通用近似式为:

微带线阻抗:

带状线阻抗:

同轴线阻抗:

经验值:

对于FR4微带线,50Ω的特征阻抗其线宽等于介质厚度的两倍,同样对于50Ω特征阻抗带状线其两平面间的总结之厚度等于线宽的两倍。

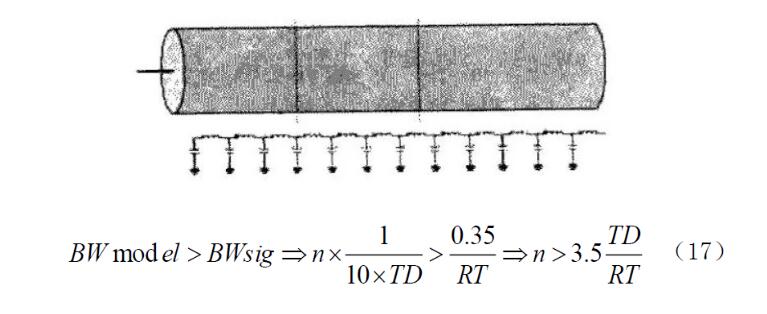

如果想获得更准确的计算特征阻抗还可以采用仿真求解方式即二维场求解器,它也是通过对传输线LC模型划分来求解,对于信号上升沿为RT,信号带宽BWsig=0.35/RT. 如果传输线的时延为TD,并用n节集总线电路模型来近似,则必须确保模型的带宽BWmodel应至少大于信号的带宽BWsig。

经验值:

当确定上升时间RT时,FR4中信号的速度大约时6in/ns,n节LC集总线模型到达到足够的带宽,每一节LC电路对应的线长必须小于1.7*RT in。

二、不同端接方式阻抗:

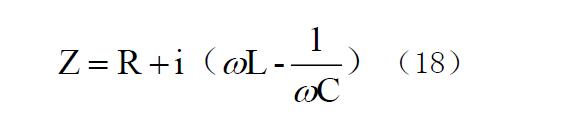

在电学中,把对电路中电流所起的阻碍作用叫做阻抗,它是一个复数。用Z表示。

具体说来阻抗可分为两个部分,电阻(实部)和电抗(虚部)。其中电抗又包括容抗和感抗,由电容引起的电流阻碍称为容抗,由电感引起的电流阻碍称为感抗。

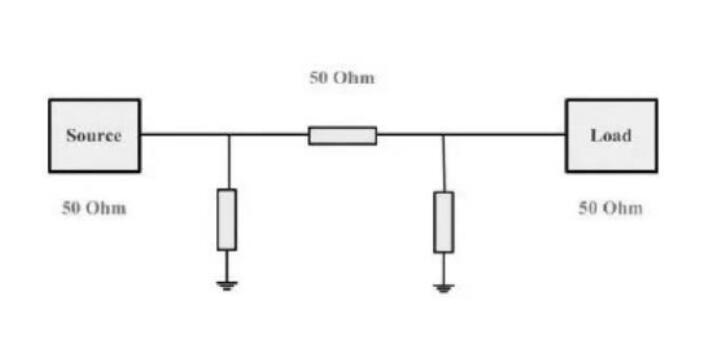

硬件工程师大都遇到过匹配阻抗的问题,通俗的讲,阻抗匹配的目的是确保能实现信号或能量从“信号源”到“负载”的有效传送。其最最理想模型当然是希望Source端的输出阻抗为50欧姆,传输线的阻抗为50欧姆,Load端的输入阻抗也是50欧姆,一路50欧姆下去,这是最理想的。

然而实际情况是:源端阻抗不会是50ohm,负载端阻抗也不会是50ohm,这个时候就需要若干个阻抗匹配电路而匹配电路就是由电阻、电容和电感所构成,这个时候就需要使用电组、电容和电感来进行阻抗匹配电路调试,以达到RF性能最优。

阻抗匹配的方法主要有两种:

Ø 改变阻抗力就是通过电容、电感与负载的串并联调整负载阻抗值,以达到源和负载阻抗匹配。

Ø 调整传输线是加长源和负载间的距离,配合电容和电感把阻抗力调整为零。此时信号不会发生发射,能量都能被负载吸收。

高速PCB布线中,一般把数字信号的走线阻抗设计为50欧姆。一般规定同轴电缆基带50欧姆,频带75欧姆,对绞线(差分)为85-100欧姆。在高速数字电路系统中,电路数据传输线上阻抗如果不匹配会引起数据信号反射,造成过冲、下冲和振铃等信号畸变,当然信号沿传输线传播过程当中,如果传输线上各处具有一致的信号传播速度,并且单位长度上的电容也一样,那么信号在传播过程中总是看到完全一致的瞬间阻抗。

减小反射的方法是根据传输线的特性阻抗在其发送端串联端接使源阻抗与传输线阻抗匹配或者在接收端并联端接使负载阻抗与传输线阻抗匹配,从而使源反射系数或者负载反射系数为零。常用的端接方式为:串联端接、并联端接、戴维南端接、RC网络端接、肖特基并联端接等。

v 串联端接:

在信号源端阻抗低于传输线特征阻抗的条件下,在信号的源端和传输线之间串接一个电阻R,使源端的输出阻抗与传输线的特征阻抗相匹配,抑制从负载端反射回来的信号发生再次反射。串联匹配是最常用的终端匹配方法。它的优点是功耗小,不会给驱动器带来额外的直流负载,也不会在信号和地之间引入额外的阻抗,而且只需要一个电阻元件。常见应用一般的CMOS、TTL电路的阻抗匹配。USB信号也采样这种方法做阻抗匹配。

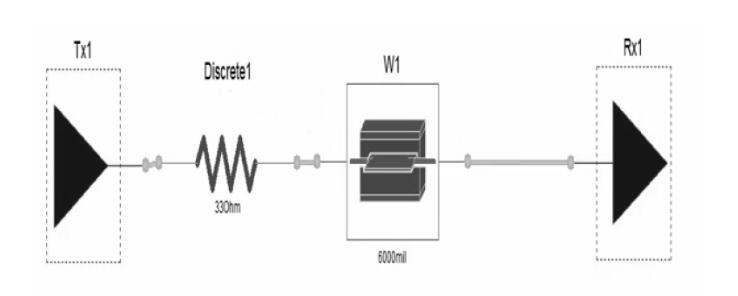

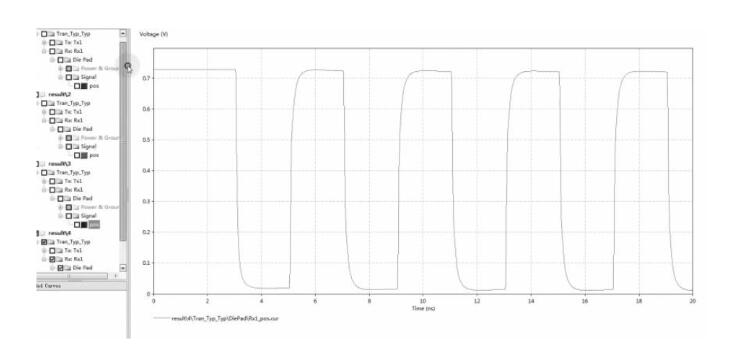

串联端接拓扑图,在传输线中串联电阻改善传输线阻抗与源端/负载端阻抗一致。

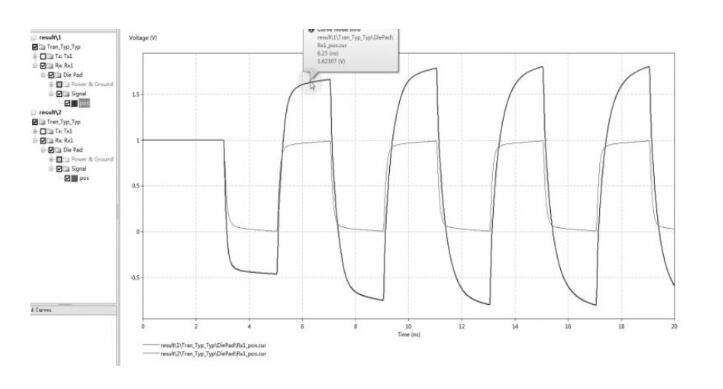

从仿真结果可以看到,阻抗匹配后信号传输无明显过冲现象。

v 并联端接:

在信号源端阻抗很小的情况下,通过增加并联电阻使负载端输入阻抗与传输线的特征阻抗相匹配,达到消除负载端反射的目的。并联终端匹配优点是简单易行,显而易见的缺点是会带来直流功耗:单电阻方式的直流功耗与信号的占空比紧密相关;双电阻方式则无论信号是高电平还是低电平都有直流功耗,但电流比单电阻方式少一半。常见应用以高速信号DDR 应用较多。

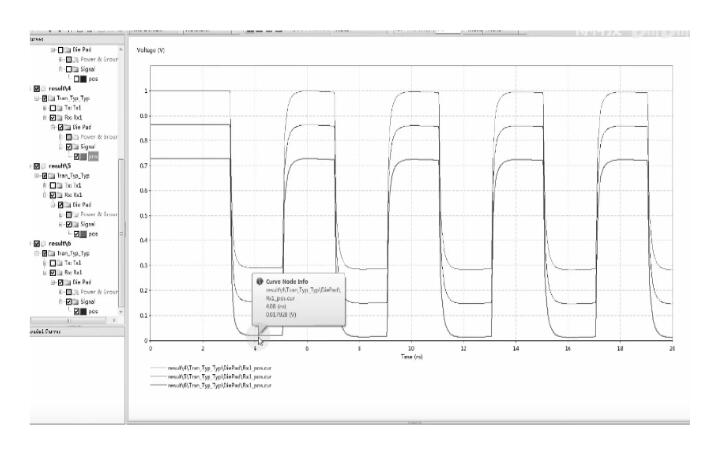

并联端接拓扑图,在传输线并联上拉或者下拉电阻保证传输线阻抗与源端/负载端阻抗一致。

从仿真结果可以看到,并联端接可以改善高/低电平。

v 戴维南端接:

上拉端接会拉高低电平,下拉端接会降低高电平,这两种端接方式虽然都可以抑制过冲和振铃,但同时也会减小信号裕量,如果使用不当还会造成信号电平的误触发。戴维南端接方式既可以抑制过冲,又没有这些缺陷。常见应用以DDR2地址、控制命令等信号。

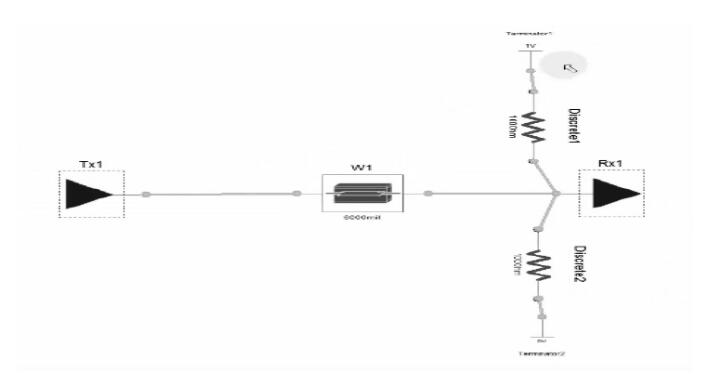

戴维南端接拓扑图,在传输线上拉和下拉电阻改善传输线阻抗与源端/负载端阻抗一致:

从仿真结果可以看到,戴维南端接可以同时改善同是高/低电平。

v RC端接:

RC端接也叫AC端接,其实就是在并联端接的基础上增加了一个电容,电容一般采用0.1uF多层陶瓷电容,由于电容通低频阻高频的作用,因此电阻不是驱动源的直流负载,故这种端接方式无任何直流功耗,交流功耗也非常小,该端接主要用于时钟电路。常见在激光驱动LD-环路中为了一致寄生电感产生的上升沿过冲问题,在回路中增加RC端接。

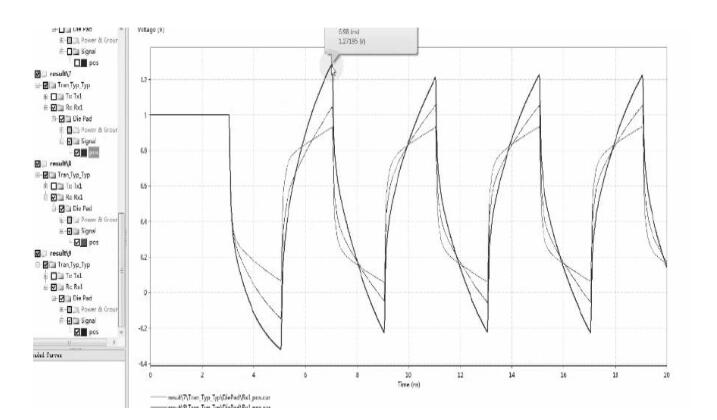

RC端接拓扑图,在传输线下拉RC串联电路改善传输线阻抗与源端/负载端阻抗一致:

从仿真结果可以看到,RC端接选择合适的RC值可以改善信号传输的过冲。

v 肖特基并联端接:

肖特基端接是在戴维南端接中将电阻换为肖特二极管并联端接,通常应用在器件内部。现在很多器件自带有输入保护二极管,该端接能有效减小信号过冲和下冲,但并不能消除反射;同时二极管的开关速度会限制响应时间,所以较高速系统不合适,一般应用与低速电路中。

肖特基并联端接拓扑图,在传输线路中并联上拉和下拉两个肖特二极管。

从仿真结果可以看到,肖特基并联端接选择合适钳位电压改善信号传输的过冲。

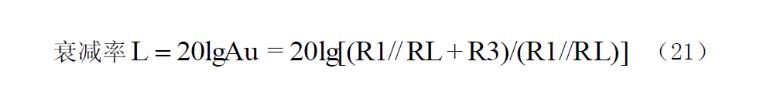

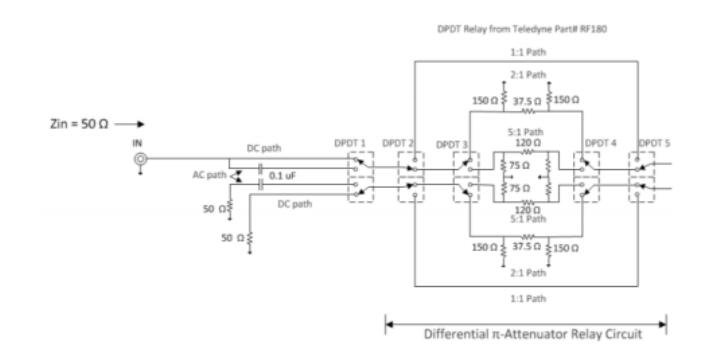

三、固定阻抗衰减器:

前面两小节讨论了传输线的阻抗理论计算和传输线阻抗的匹配,在实际工作应用中经常会遇到即需要满足设计要求达到信号衰减并同时满足阻抗匹配要求,这时就需要一种方便通用的固定阻抗衰减器(π型衰减器)。它主要作用是对信号进行衰减处理和阻抗匹配,同时满足调整负载功率和抑制信号反射。

衰减器对信号功率进行衰减必须进行阻抗匹配,不然就会形成驻波或者反射。所以衰减器的输入端要与信号源的输出阻抗(内阻)匹配;输出端要与负载阻抗匹配;负载阻抗要和传输线的特征阻抗相等,此时的传输不会产生反射,这表明所有能量都被负载吸收了。所以输入阻抗、输出阻抗、信号源内阻、负载阻抗、线路特征阻抗皆为50Ω。

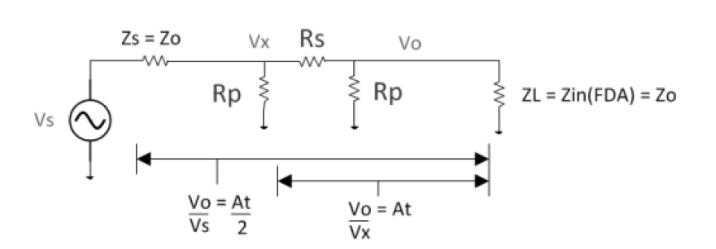

π型衰减器拓扑图,在源端和负载端串联一个电阻同时在源端和负载端同时下拉相同电阻。

其中RL为负载电阻,r为信号源内阻;

推导可得:

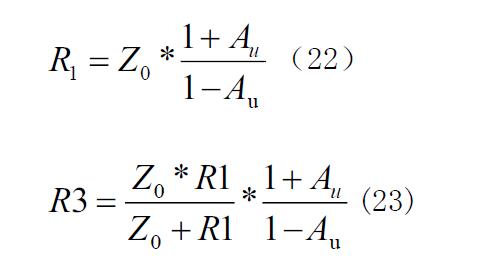

在高速电路的数据采集电路中,源端信号为一个宽输入信号,接收端为高带宽高采样率的高度信号采集卡,而对于CMOS电路而言熟知的带宽增益积为固定值。高速高精度采集卡输入范围比较小,这时为了更好的匹配源端和后端信号,需要对于源端信号做前级调理AFE电路,下图摘自TI官网的某个AFE典型应用电路。

从电路图中可以看到输入阻抗为50欧姆,DC耦合和AC耦合通道首先经过DPDT1开关选择后到DPDT2/3/4不同通道的差分π型衰减器做信号匹配和衰减后从DPDT5输出阻抗差分阻抗为100Ω(单端为50Ω)。

对上述AFE电路做参数提取,即为一个标准的单端π型网络。

按照2:1衰减路径计算,输入输出阻抗为50Ω,代入公式(22)(23)可得:

常用固定衰减器还有L型、T型、X型和桥T型等几种结构,计算方案与π型衰减器类似,这里不再赘述。

总结一下,对于高速信号传输而言既要扎实学习各部分理论知识和概念,也要在学习工作中总结经验熟练仿真软件,从电路和电磁场角度不断深入求索才能逐步得心应手。